For customers designing NXP Semiconductors Kinetis K

我们很高兴向您介绍我们的晶体单元。

确认事项(振荡电路设计)

请注意:设计振荡电路需要确认如下电子特性:

振荡裕度和负电阻(-R):

您需要确认振荡能力。

我们建议条件:(-R)/ ESR > 5

* -R:负电阻,ESR:等效串联电阻

驱动级别:

需要确认振荡是否稳定,驱动水平是否在规格范围内。

负载电容:

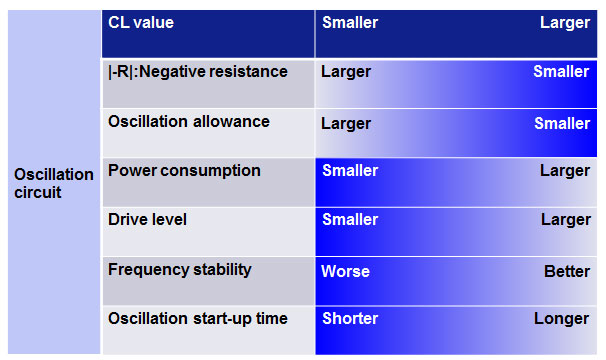

负载电容影响频率稳定性、振荡余量、负电阻和振荡启动时间。

此外,负载电容是晶体单元的负载电容(CL值)的决定因素。

有关每个特性的详细信息,请参阅 PDF 文件。

振荡电路设计注意事项晶体单元选择指南

客户在选用晶体单元时,负载电容(CL值)是选择的重要因素。例如,CL较小的晶体(7.0 pF)振荡裕度较大,电流消耗较小,频率稳定性较差,如下表所示。

相反,CL较大的晶体(12.5 pF)振荡裕度较小,消耗电流较大,频率稳定性较好,选择时请充分考虑这些特性。

爱普生水晶产品系列

| Product | Size[mm] | Applications | Images |

|---|---|---|---|

| FC-135 | 3.2 x 1.5 x 0.9 |

PMP, DSC, Portable equipment |  |

| FA-238 FA-238V |

3.2 x 2.5 x 0.7 | - Mobile phone, Bluetooth, W-LAN - ISM band, Clock for MPU |

|

Kinetis K应用处理器的振荡电路及晶体单元选型指导

1)32千赫

内部可编程电容:0(实时时钟控制寄存器=0,默认)

| IC name | Epson Product | External parts *3 | |||||

|---|---|---|---|---|---|---|---|

| Product name | Freq. [Hz] |

CL *1 [pF] |

Product Code *2 | Package size WxDxH [mm] |

Cg [pF] |

Cd [pF] |

|

| MK60DN512ZVLQ10 | FC-135 | 32.768k | 12.5 | Q13FC13500002** | 3.2 x 1.5 x 0.9 | 18 | 15 |

2)24MHz

内部可编程电容:0(实时时钟控制寄存器=0,默认)

| IC name | Epson Product | External parts *3 | ||||||

|---|---|---|---|---|---|---|---|---|

| Product name | Freq. [Hz] |

CL *1 [pF] |

Product Code *2 | Package size WxDxH [mm] |

Cg [pF] |

Cd [pF] |

Rd [Ω] |

|

| MK10FX512VLQ12 | FA-238V | 12M | 10.0 | Q22FA23V00019 | 3.2 x 2.5 x 0.7 | 10 | 10 | 1000 |

| MK50DX256ZCLL10 | FA-238 | 16M | 10.0 | Q22FA23800421 | 3.2 x 2.5 x 0.7 | 10 | 10 | 1000 |

| MK60DN512ZVLQ10 | FA-238 | 20M | 10.0 | Q22FA23800264 | 3.2 x 2.5 x 0.7 | 5 | 5 | - |

Notes:*

*1.负载电容.

*2.产品代码的两位数字是包装规格,详情请参考此处。

*3.以上建议基于实际评估结果,旨在支持用户选择正确的组件。作为实际的电路板布局和外部元件的选择。由于实际的电路板布局和外部组件的选择会影响最合适的晶体负载电容,因此我们不对上述建议承担任何责任并授予保修。用户的设计必须通过自己和个人的评估来验证和决定。

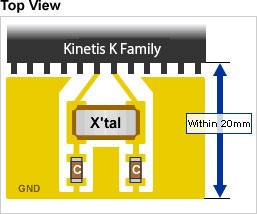

PCB板设计注意事项

引脚、晶体单元、电容器和电阻器的布局

-请尽可能将晶体单元、电容器和电阻器布置在靠近Kinetis K系列的地方。

-振荡电路中的信号线长度应尽可能短,并且不要与其他信号线交叉。

用于 32 千赫晶体单元

PCB 的GND线图案和互连

-请在晶体单元下方布置GND线路图案。

-如果是多层PCB板,请不要在晶体单元下方布置其他信号线。