FAQ

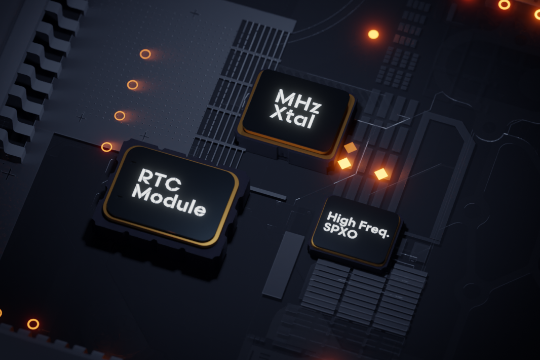

RX-8571SA/NB/LC

QVLFビット(Voltage Low Flag)が1になる条件を教えてください。

以下の3つの条件です。

- (1) 初期電源投入時。

- (2) 衝撃や電圧低下で内蔵の水晶発振が約10ms以上停止した場合。(電圧監視ではありません)

- (3) VDDのtF,tRが弊社規定(マニュアル記載)よりも早いときにセットされる場合があります。

Q周波数偏差にあるΔf/f=5±23ppmの5ppmを教えてください。

5ppmはオフセット値となります。このオフセット値を設定する理由は以下のとおりです。

内蔵の水晶振動子は、周波数に対して温度特性を持っており、以下のように+25±5℃を頂点にマイナスの2 次曲線になります。+25℃に対して低い温度であっても高い温度であっても発振周波数が低くなる特性を持っています。よって、平均温度が+25℃でない雰囲気中で時計内蔵の機器を使用した場合、すべて時計が遅れてしまいます。

この遅れを少しでも解消する目的のためオフセットを設定しています。

Q分単位でタイマーを使用すると初回動作時は1分よりも早いタイミングで出力されます。 この原因について教えてください。

分単位のタイマーは内部の時計機能の分桁更新を利用しているため初回動作のタイミングは1分よりも早く出力されます。例えば内部計時が40秒のときに"1分後"のタイマー設定した場合約20秒後に分桁が更新されてタイマー割込みが発生します。

QRTCモジュールをキャパシタでバックアップしているため、電源を落とすことはできません。電源をOFFしないまま、I²Cバスを解放する手段は有りますか?

SCLラインが制御できる場合は、SCLにクロックを送信し続けることでSDAが解放されます。

その後STOPコンディションを送信することで新たな通信が開始可能となります。

Q配線パターン設計で注意する点はありますか?(対象:SAパッケージ)

アプリケーションマニュアルの取り扱い上の注意事項をご確認願います。

またSAタイプとSJタイプにつきまして、補足説明資料を合わせてご確認願います。